# NetBurner FPGA Blade Board (NBPKX500-100CR) Manual

#### **Table of Contents**

| 1 | Intro | duction                                                  | . 3 |

|---|-------|----------------------------------------------------------|-----|

|   | 1.1   | Overview                                                 | . 3 |

|   | 1.2   | Features                                                 | . 3 |

|   | 1.3   | Requirements                                             | . 4 |

|   | 1.4   | Design Outline                                           | . 4 |

| 2 | Prog  | ramming the FPGA                                         |     |

|   | 2.1   | Create the Verilog and User Constraints Files            | . 4 |

|   | 2.2   | Compile the source files using Xilinx tools              | . 4 |

|   | 2.3   | Making a bitstream file                                  | . 9 |

|   | 2.4   | Convert the bit file to a cpp to be used by your project | . 9 |

|   | 2.4.1 | Using NBEclipse                                          | . 9 |

|   | 2.4.2 | 2 Using the command line                                 | 10  |

|   | 2.5   | Add the source files to your project                     | 10  |

|   | 2.6   | Call LoadCode on startup                                 | 11  |

|   |       |                                                          |     |

# **Revision History**

| Rev. | Date   | Comments             |

|------|--------|----------------------|

| 1.0  | 6/2010 | Initial release      |

| 1.1  | 2/2011 | Revised introduction |

## 1 Introduction

Special Note:

This documentation will detail the process of creating, building, and loading code to an FPGA running on the FPGA Blade Board. It is not an instructional document on Verilog or VHDL programming, and only covers how to load your source into the NetBurner tools. If you are using the Xilinx Design Suite, you must download the software directly from Xilinx.

### 1.1 Overview

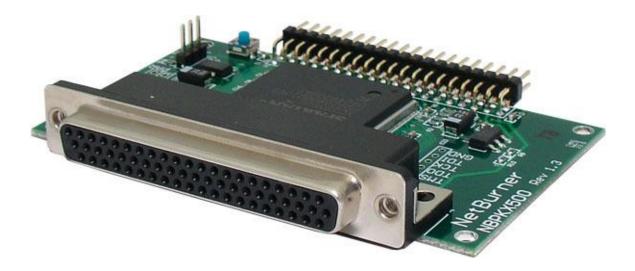

The FPGA blade board is development hardware that enables a developer to quickly interface a PK70 with a Spartan 3E FPGA. Using NetBurner tools and this guide, learn how Xilinx binary files can be loaded directly in to a NetBurner project. The NetBurner project can then load the binary file on to the FPGA at runtime, keeping your application and FPGA blade board in sync.

### 1.2 Features

- Hardware layout featuring access to the Xilinx Spartan 3E FPGA

- Parallel interface between the Spartan 3E and a NetBurner PK70 device

- High Density 62 pin connector (DB-62HD)

- Program the FPGA anytime with the JTAG connector or at runtime from a NetBurner application

- Code examples demonstrating how to load an FPGA binary file at runtime

#### 1.3 Requirements

The following hardware and software is required to use this guide

- NetBurner NNDK version 2.4 or greater

- NetBurner PK70 device

- NetBurner FPGA Blade Board

- Xilinx ISE Design Suite

#### 1.4 Design Outline

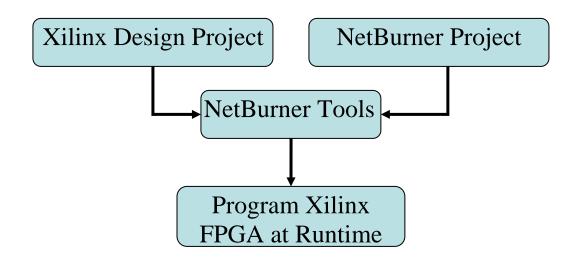

Creating a project for the Xilinx FPGA consists of three major steps:

- 1. Compiling the Verilog source in to a BIT file

- 2. Converting the BIT file in to a C++ source file. This file can be used by any NetBurner project.

- 3. Call a special function which loads the FPGA source from the NetBurner application.

This document will go over the steps needed to be taken to complete this process. Source files will be provided to create a simple GPIO demo.

## 2 Programming the FPGA

#### 2.1 Create the Verilog and User Constraints Files

The first step in building for the FPGA blade board is to create your Verilog and User Constraints file. An example Verilog source file and user constraints file has been included with the board. To follow along in this Users Guide, you should use these examples, XilinxBladeGpio.v and XilinxBlade.ucf.

#### 2.2 Compile the source files using Xilinx tools

To compile the source files, you must have the Xilinx tools installed. In this example, I used the Xilinx ISE Design Suit, 12.1. Different versions of the tools may produce different results.

To start, click on the start menu and select Xilinx ISE Design suite  $12.1 \rightarrow$  ISE Design Tools  $\rightarrow$  Project Navigator. You should now be at the main ISE screen (Figure 2.2-1)

| 🗾 ISE Project Navigator (M.53d) - [ISE Design Suite InfoCent | ter]                                                                                                                                                                                                             | • • <mark>• ×</mark> |

|--------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| Eile Edit View Project Source Process Jools                  | Window Layout Help                                                                                                                                                                                               | _ 8 ×                |

|                                                              | P P B B P B 🕅 🖻 🗉 🖻 🕨 🛠 🕨 🛛 🛠                                                                                                                                                                                    |                      |

| Start ↔ 🗆 🗗 🗙 🙆                                              |                                                                                                                                                                                                                  |                      |

| Use one of the options below to start working on a           | Release Overview Design Resources Documentation Project Navigator                                                                                                                                                |                      |

| for more information.                                        | ISE Design Suite 12 Release Overview                                                                                                                                                                             |                      |

| P                                                            | ISE Design Suite Highlights:                                                                                                                                                                                     |                      |

| Recent projects                                              | <ul> <li>Xilinx® ISE® Design Suite 12 enables dynamic power reduction using patent pending automated clock gati</li> <li>Design preservation flow for timing predictability.</li> </ul>                          | ing technoli         |

| Double dick on a project in the list below to open           | XXI-4 compliant IP supports a streamlined "plug-and-play" FPGA design flow Coming in Fall 2010     Intuitive 4th generation partial reconfiguration design flow for Virtex®-6 enables lower system costs and pov | wer.                 |

|                                                              | <ul> <li>System Generator support for Windows@XP and VISTA@64-bit.</li> <li>High density design will see 2X faster synthesis and 1.3X faster implementation runtimes.</li> </ul>                                 | E                    |

|                                                              | IP Updates: Click here for a summary of IP library updates and new products.                                                                                                                                     |                      |

| Project commands Open Project Project Browser                | Ease of Use: Click the Documentation tab to quickly locate important ISE documentation resources.                                                                                                                |                      |

| New Project Open Example                                     | Resources                                                                                                                                                                                                        |                      |

|                                                              | What's New in Xilinx ISE Design Suite                                                                                                                                                                            |                      |

| Additional resources                                         | <ul> <li>Xilinx ISE Design Suite 12 Installation, Licensing, and Release Notes</li> </ul>                                                                                                                        |                      |

| ISE Design Suite InfoCenter                                  | <ul> <li>Known issues in the Xilinx ISE Design Suite 12 Release</li> <li>Online Stude duith the ISE Design Suite 14 Release</li> </ul>                                                                           |                      |

| ISE Ouick Start<br>Tutorials on the Web                      | <ul> <li>Getting Started with the ISE Design Suite Tutorials</li> </ul>                                                                                                                                          |                      |

| Application Notes                                            | For a complete list of Xilinx ISE Design Suite 12 documentation, refer to the Documentation tab                                                                                                                  | •                    |

| Ist                                                          | ISE Design Suite InfoCenter                                                                                                                                                                                      |                      |

| Console                                                      |                                                                                                                                                                                                                  | ↔□♂>                 |

|                                                              |                                                                                                                                                                                                                  |                      |

|                                                              |                                                                                                                                                                                                                  |                      |

|                                                              |                                                                                                                                                                                                                  | ÷.                   |

| Console Console Console Console Console                      | Results                                                                                                                                                                                                          |                      |

Figure 2.2-1

Click on the New Project button to start a new project (Figure 2.2-2)

| Mew Project          | Wizard                                                 | x           |

|----------------------|--------------------------------------------------------|-------------|

| Create New Pro       |                                                        |             |

| Enter a name, locati | ons, and comment for the project                       |             |

| N <u>a</u> me:       | XilinxBladeDemo                                        |             |

| Location:            | C: \nburn \examples \pk70 \xilinx \XilinxBladeDemo     |             |

| Working Directory:   | C: \nburn \examples \pk70 \xilinx \XilinxBladeDemo     | <u></u>     |

| <u>D</u> escription: | A Demo of how to use the Xilinx FPGA blade on the PK70 |             |

|                      | p-level source for the project                         |             |

| Top-level source typ | e:                                                     |             |

| More Info            |                                                        | Next Cancel |

Figure 2.2-2

After naming your project, click next to bring up the project settings. (Figure 2.2-3) Fill in the device type as XC3S500E in the PQF208 package.

| Project Settings                                                                      |                     |   |

|---------------------------------------------------------------------------------------|---------------------|---|

|                                                                                       |                     |   |

| Specify device and project properties.<br>Select the device and design flow for the p | roject              |   |

|                                                                                       | Value               |   |

| Property Name                                                                         |                     |   |

| Product Category                                                                      | All                 | _ |

| Family                                                                                | Spartan3E           | _ |

| Device                                                                                | XC3S500E            |   |

| Package                                                                               | PQ208               |   |

| Speed                                                                                 | -5                  |   |

| T 1 10 T                                                                              | HDI                 |   |

| Top-Level Source Type                                                                 |                     | _ |

| Synthesis Tool                                                                        | XST (VHDL/Verilog)  | _ |

| Simulator                                                                             | ISim (VHDL/Verilog) |   |

| Preferred Language                                                                    | Verilog             |   |

| Property Specification in Project File                                                | Store all values    |   |

| Manual Compile Order                                                                  |                     |   |

| VHDL Source Analysis Standard                                                         | VHDL-93             |   |

|                                                                                       |                     |   |

Figure 2.2-3

Click next to proceed to the project summary page. (Figure 2.2-4) Verify that the proper device and package is selected and click finish to create the project.

|                                                                                | ×     |

|--------------------------------------------------------------------------------|-------|

| New Project Wizard                                                             |       |

| Project Summary                                                                |       |

| Project Navigator will create a new project with the following specifications. |       |

| Project:                                                                       |       |

| Project Name: XilinxBladeDemo                                                  |       |

| Project Path: C:\nburn\examples\pk70\xilinx\XilinxBladeDemo                    |       |

| Working Directory: C:\nburn\examples\pk70\xilinx\XilinxBladeDem                | o 🛛   |

| Description: A Demo of how to use the Xilinx FPGA blade on the                 | PK70  |

| Top Level Source Type: HDL                                                     |       |

| Device:                                                                        |       |

| Device Family: Spartan3E                                                       |       |

| Device: xc3s500e                                                               |       |

| Package: pq208                                                                 | E     |

| Speed: -5                                                                      |       |

| Synthesis Tool: XST (VHDL/Verilog)                                             |       |

| Simulator: ISim (VHDL/Verilog)                                                 |       |

| Preferred Language: Verilog                                                    |       |

| Property Specification in Project File: Store all values                       |       |

| Manual Compile Order: false                                                    |       |

| VHDL Source Analysis Standard: VHDL-93                                         |       |

| Message Filtering: disabled                                                    | -     |

| More Info                                                                      | ancel |

Figure 2.2-4

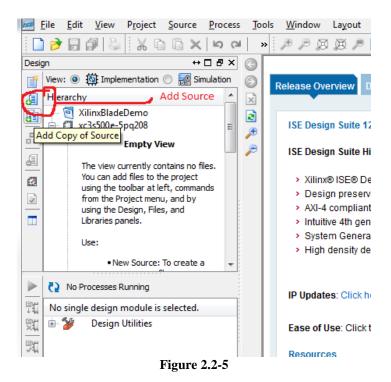

Once the project has been created, you must add the project files that we are building in this examples, XilinxBladeGpio.v and XilinxBlade.ucf. Begin by copying them into your project folder. Next, add them to the project by clicking on the add source project button. (Figure 2.2-5)

Clicking on the add source button brings up a file dialog. After adding the source, you should be back in the project summary screen. (Figure 2.2-6)

| 2        | Eile Edit ⊻iew Project Source Proces                     | -<br>  14                                                                        | * / / / Ø Ø /                    | Help            | I 🕒 🎤 K?                                  | ► ∑ <b>1</b> | •         |                       |               |             | - 8       |

|----------|----------------------------------------------------------|----------------------------------------------------------------------------------|----------------------------------|-----------------|-------------------------------------------|--------------|-----------|-----------------------|---------------|-------------|-----------|

| Desi     |                                                          | i 🄥                                                                              | Design Overview     Summary      | _               |                                           | Xili         | nxBlade(  | pio Project           | Status        |             |           |

| ľ        | View:      View:      Implementation      Implementation |                                                                                  | IOB Properties                   |                 | Project File:                             | XilinxBlad   | eDemo.xis | Parser                | Errors:       |             | No Errors |

| 6        | Hierarchy                                                | 6                                                                                | 🛄 Module Level                   |                 | Module Name:                              | XilinxBlad   | eGpio     | Imple                 | nentati       | on State:   | New       |

| 8        | XilinxBladeDemo                                          |                                                                                  | Timing Constr<br>Pinout Report   |                 | Target Device:                            | xc3s500e     | -5pq208   |                       | Errors:       |             |           |

|          | XCSS00e-Spq208     XilinxBladeGpio (XilinxBla            | Ç                                                                                | Clock Report                     |                 | Product Version:                          | ISE 12.1     |           |                       | Warnin        | gs:         | -         |

|          |                                                          | Static Timing<br>- Errors and Warnings<br>Static Timing<br>- Errors and Warnings |                                  |                 | Design Goal:                              | Balanced     |           |                       | Routing       | Results:    |           |

| 6        |                                                          |                                                                                  |                                  | ner E           | Design Strategy: Xlinx Default (unlocked) |              | (ed)      | • Timing Constraints: |               |             |           |

|          |                                                          | A                                                                                | Synthesis Mes                    |                 | Environment:                              | _            |           |                       | -<br>Final Ti | ming Score: |           |

|          |                                                          | 140                                                                              | - Translation Me                 |                 |                                           |              |           |                       |               | -           | _         |

|          |                                                          |                                                                                  | 🗋 Map Message<br>📄 Place and Rou | ite Messages    |                                           |              | Detailed  | Reports               |               |             | F         |

|          |                                                          | E                                                                                | Timing Messa                     |                 | Report Name                               |              |           | Generated             | Errors        | Warnings    |           |

|          |                                                          |                                                                                  |                                  | tation Messages | Synthesis Report                          |              |           |                       |               |             |           |

| -        |                                                          | 1                                                                                | Detailed Reports                 |                 | Translation Report                        |              |           |                       |               |             |           |

| ₽        | No Processes Running                                     | 2                                                                                | Synthesis Repo                   |                 | Map Report                                |              |           |                       |               |             |           |

| 70       | Processes: XilinxBladeGpio                               |                                                                                  | 🗋 Map Report                     |                 | Place and Route Re                        | port         |           |                       |               |             |           |

| <u>S</u> | Design Summary/Reports                                   | ŧ.                                                                               | Place and Rou                    | ite Report 🚽    | Power Report                              |              |           |                       |               |             |           |

| 91       | User Constraints                                         |                                                                                  | Design Properties                |                 | Post-PAR Static Tim                       | ing Report   |           |                       |               |             |           |

|          | 🐵 🚺 Synthesize - XST                                     |                                                                                  | Optional Design Summary          |                 | Bitgen Report                             |              |           |                       |               |             |           |

|          | Implement Design     Generate Programming File           |                                                                                  | Show Clock Repor                 |                 |                                           |              |           |                       |               |             |           |

|          | Configure Target Device                                  |                                                                                  | Show Failing Cons                | straints        |                                           |              |           |                       |               |             |           |

|          | Analyze Design Using ChipScope                           |                                                                                  | Show Warnings                    |                 |                                           | 5            |           | ary Reports           |               |             | E         |

|          |                                                          |                                                                                  |                                  |                 | Report Name                               |              | Status    |                       | Gen           | erated      |           |

|          |                                                          |                                                                                  |                                  |                 |                                           | Date (       | Generate  | <b>d:</b> 05/26/2010  | - 16:33:      | 36          |           |

| 152      | Start 🕫 Design 🖺 Files 🚺 Libraries                       | 152                                                                              | ISE Design Suite InfoCe          | enter 🗵 🗵       | Design Sum                                | nary         | ×         |                       |               |             |           |

| Con      | sole                                                     |                                                                                  |                                  |                 |                                           |              |           |                       |               |             | ⇔⊡ 8      |

| 4        | ш                                                        |                                                                                  |                                  |                 |                                           |              |           |                       |               |             | 4         |

Figure 2.2-6

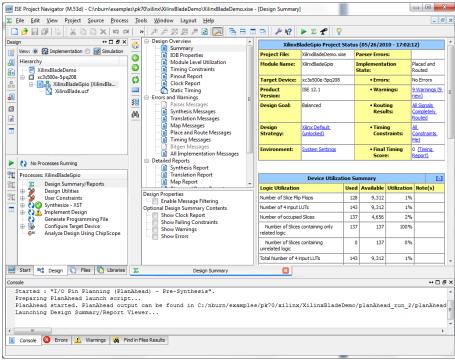

Click on the green arrow next to No Processes Running text to start the build. (Figure 2.2-7)

Figure 2.2-7

You may get some warning about drivers on the debug connector and a misplaced clock. It's safe to ignore these warnings.

#### 2.3 Making a bitstream file

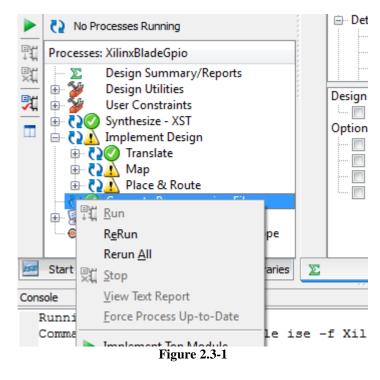

Create the bitstream file by opening the implement design tree item in the process window. Right click on Generate Programming File and choose run. (Figure 2.3-1)

This creates the bit file, xilinxbladegpio.bit

### 2.4 Convert the bit file to a cpp to be used by your project

To convert the bit file into a cpp that can by compiled and linked in to your project, you must use two utilities, promgen and compfile. We will go over how to do this in both NBEclipse and building on the command line.

#### 2.4.1 Using NBEclipse

NBEclipse will automatically convert and use the bit file. Simply drop the file in to your project. NBEclipse will recognize bit files and use the promgen and compfile utilities to build the cpp source file XilinxImage.cpp, which will be used by your project.

If you need to change the command line options used by promgen or compfile, right click on your project and select Properties. Under C/C++ Build, select Settings. You will find the options for promgen and compfile here.

#### 2.4.2 Using the command line

To convert the bit file manually, you will need to call promgen to convert the file from a bit to a bin, and then compfile to convert from bin to a cpp.

Convert the bit file to a prom file:

promgen -w -p bin -c FF -o BinPromImage -u 0 xilinxbladegpio.bit -s 65536

Convert the bin file to a CPP file we can link to our project:

compfile BinPromImage.bin XilinxData XilinxSize XilinxImage.cpp

You can use promgen --help and compfile --help to examine the various command line options you can use to affect the build.

### 2.5 Add the source files to your project

Three source files must now be added to your NetBurner project to finish the build. First, add the cpp file that was generated in the last section, (2.4) XilinxImage.cpp. If you are following along in NBEclipse, this file will automatically be included, and can be found in your release directory.

Next, add the files LoadCode.cpp and LoadCode.h. These files were included in the FPGA Blade Board release files. These will allow your application to load the FPGA source while your application is running.

#### 2.6 Call LoadCode on startup

Finally, you will need to tell the application to load the Xilinx FPGA with the stored code. This is done with the LoadCode function. You will also have to set up any required chipselects for talking to the device.

BOOL result = LoadCode();

The final results, if you are using the example files provided would be as follows:

Waiting 1sec to start 'A' to abort Configured IP = 10.1.1.73Configured Mask = 255.255.255.0MAC Address= 00:03:f4:02:f8:2dAbout to Load Code Took 2 ticks Load Code Result = 1Locations readback 123ABC In the example project this should be 123ABC Wait....hit a key

So if what we readback matches what it should be in the line below, the FPGA loaded correctly.

#### **Disclaimers and Copyrights**

NetBurner, Inc. makes no representations or warranties with respect to the contents of our manuals and specifically disclaims any implied warranties of merchantability or fitness for any particular purpose. Further, NetBurner, Inc. reserves the right to revise our manuals, make changes, and/or discontinue them without notice. Every effort has been made to ensure that all information is correct, but NetBurner, Inc. is not responsible for inadvertent errors.

NetBurner manuals contain links to third-party web sites that are not under the control of NetBurner, and NetBurner is not responsible for the content on any linked site. If you access any third-party sites listed in any of our manuals, then you do so at your own risk. NetBurner provides these links only as a convenience, and the inclusion of the link does not imply that NetBurner endorses or accepts any responsibility for the content on those third-party sites.

Under copyright laws, the documentation for the all NetBurner Manuals, PDFs, and Guides may not be copied, photocopied, reproduced, translated or reduced to any electronic medium or machine-readable form, in whole or in part, without prior written consent of NetBurner, Inc. NetBurner and the NetBurner logo are trademarks of NetBurner, Inc.

#### Life Support Disclaimer

NetBurner's products both hardware and software (including tools) are not authorized for use as critical components in life support devices or systems, without the express written approval of NetBurner, Inc. prior to use.

As used herein: (1) Life support devices or systems are devices or systems that (a) are intended for surgical implant into the body or (b) support or sustain life, and whose failure to perform, when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user. (2) A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.