**V**et Burner

# Mod5282 Hardware Design Notes

# **Application Note**

Revision 1.0 January 27, 2004 Document Status: Release

# **Table of Contents**

| 3 |

|---|

| 3 |

| 3 |

| 4 |

| 4 |

| 4 |

| 5 |

| 5 |

| 6 |

| 6 |

| 6 |

|   |

# Introduction

This document provides hardware design information, tips and guidelines for using the Mod5282 with external hardware. This document uses the following terminology:

Output: indicates an output from the microprocessor. Please reference the electrical characteristics for the specific signal in the Motorola ColdFire 5282 User's Manual.

Input: indicates an input to the Mod5282. Most inputs will have a pull-up resistor as indicated.

Asserted: The asserted state of a signal depends upon the signal description. If a signal is active low as defined by the '\*' character preceding the signal name, then the asserted state is low. If a signal is active high, then the asserted state is high.

Negated: The negated state of a signal depends upon the signal description. If a signal is active low as defined by the '\*' character preceding the signal name, then the negated state is high. If a signal is active high, then the negated state is low.

### **Interrupt Signals**

Four interrupt signals are available on connector J2: \*IRQ1, \*IRQ3, \*IRQ5 and \*IRQ7. These signals are inputs pulled to 3.3V through individual 4.7K resistors.

# QSPI

The QSPI signals are configured as show in the table below.

| Signal   | Description                       |

|----------|-----------------------------------|

| SPI_CLK  | Output. Serial clock              |

| SPI_DIN  | Floating Input. Serial data input |

| SPI_DOUT | Output. Serial data output.       |

| *SPI_CS0 | Output. Peripheral chip select.   |

| *SPI_CS1 | Output. Peripheral chip select.   |

| *SPI_CS2 | Output. Peripheral chip select.   |

| *SPI CS3 | Output. Peripheral chip select.   |

# **Analog to Digital Inputs**

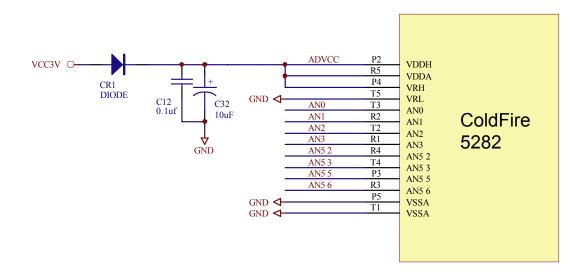

The Mod5282 has 8 ADC inputs. These signals go direct to the processor – there is no filtering circuitry on the module. The ADVCC reference input signal on the Mod5282 is tied to 3 inputs on the processor: VDDH, VDDA and VRH as shown below. Note that the diagram below shows the circuitry on the Mod5282, not the development board.

If you do not connect a reference voltage to ADVCC, then the reference will run from the 3.3V rail through the diode. Alternatively, you can connect your own reference of up to 5VDC to ADVCC.

#### **Chip Selects**

The chip selects \*CS1, \*CS2 and \*CS3 are outputs.

#### **Reset Signals**

| Signal | Description  | Implementation                                                                                                       |

|--------|--------------|----------------------------------------------------------------------------------------------------------------------|

| *RSTI  | Reset Input  | Input with 4.7k pull-up to 3.3V. Asserted to enter reset                                                             |

|        |              | exception processing.                                                                                                |

| *RST0  | Reset Output | Output from processor. Automatically asserted with<br>*RSTI. Negation indicates that the PLL has regained it's lock. |

# **Bus Control Signals**

| Signal     | Description          | Implementation                                              |

|------------|----------------------|-------------------------------------------------------------|

| R/*W       | Read/Write           | Output. Indicates the direction of the data transfer on the |

|            |                      | bus.                                                        |

| *OE        | Output Enable        | Output. Indicates when an external device can drive data    |

|            |                      | on the bus.                                                 |

| *BS2, *BS3 | Byte strobes         | Output. Defines the byte lane of data on the data bus.      |

| *TIP       | Transfer in Progress | Output. Asserted to indicate a bus transfer is in progress. |

|            |                      | Negated during idle bus cycles.                             |

| *TA        | Transfer Ack         | Input with 4.7k pull-up to 3.3V. Indicates that the         |

|            |                      | external data transfer is complete and should be asserted   |

|            |                      | for one clock.                                              |

| *TEA       | Transfer Error Ack   | Input with 4.7k pull-up to 3.3V. Indicates than an error    |

|            |                      | condition exists for the bus transfer.                      |

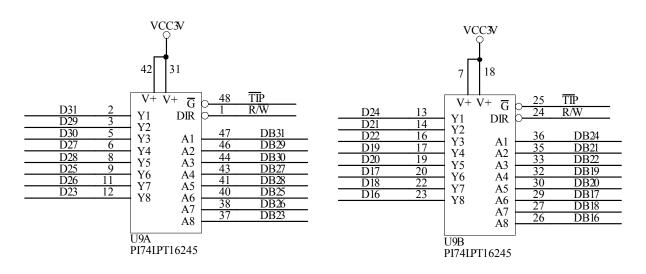

#### TIP Signal and External Data Bus Connections

The \*TIP signal can used to control an external data bus buffer for the data bus signals. An example circuit design can be found on the Module Development Board schematic. An external data bus buffer is recommended for any designs that use data bus signals D16 - D31

# System Clock Signal

The system clock pin provides an output of 66.355 MHz. The system clock on the Mod5282 is derived from a 3.6864 MHz crystal, which is fed into the ColdFire 5282 PLL.

### UARTS

The Mod5282 has 3 UARTs, designated as UART 0, UART 1 and UART 2. All the UART signals go direct to the 5282 processor. It is recommended that you include a pull-up resistor of 10k ohms for any UART RX signals that are not used (either as UARTs or an alternate function).

The third UART interface, designated as UART 2, can be configured by the 5282 processor to use either the I2C pins, or the CAN pins.

The NNDK Module Development Board has 330 ohm resistors in series with the UART RX lines. This was done to make the development board compatible with the ColdFire 5282, which has a maximum current specification of 25mA if the input voltage is above 3.3VDC. The resistors are not required for the ColdFire 5272. The resistors are present on board revisions 1.1 and later. If you are designing exclusively with the Mod5282, then the use of a 3.3V transceiver is recommended.

# **CAN Interface**

The CAN signals are routed directly from the 5282 processor.